# Article Application of CMOS Technology to Silicon Photomultiplier Sensors

Nicola D'Ascenzo \*,<sup>†</sup>, Xi Zhang <sup>†</sup> and Qingguo Xie \*,<sup>†</sup>

School of life science and technology, Huazhong University of Science and Technology, Wuhan 430073, China; dhmo@hust.edu.cn

\* Correspondence: ndasc@hust.edu.cn (N.D.); qgxie@hust.edu.cn (Q.X.); Tel.: +86-27-8779-2294 (N.D. & Q.X.)

+ These authors contributed equally to this work.

Received: 7 September 2017; Accepted: 21 September 2017; Published: 25 September 2017

**Abstract:** We use the 180 nm GLOBALFOUNDRIES (GF) BCDLite CMOS process for the production of a silicon photomultiplier prototype. We study the main characteristics of the developed sensor in comparison with commercial SiPMs obtained in custom technologies and other SiPMs developed with CMOS-compatible processes. We support our discussion with a transient modeling of the detection process of the silicon photomultiplier as well as with a series of static and dynamic experimental measurements in dark and illuminated environments.

**Keywords:** silicon photomultiplier; avalanche detection structures; geiger mode; low photon flux sensors

# 1. Introduction

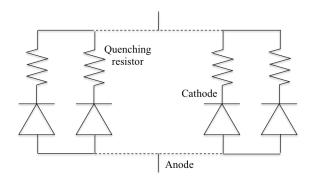

The application of silicon technology to the development of low photon flux sensors—later known as silicon photomultipliers (SiPMs)—can be traced back to the late 1970s [1], when a space-distributed fine array of metal resistor semiconductor (MRS) micro-sensors was conceived with individual quenching and common output. Since then, the SiPM R&D is dominating the panorama of modern research in the field of low photon flux detectors, with the synergy and unique contribution of a large number of groups during the last 30 years [2–10]. Modern SiPMs are composed of an array of p/n-junctions (microcells) operated in Geiger mode, with individual passive quenching resistors, as reported in Figure 1. SiPM exhibits a clear response to single photons and an impressive photon number resolution at room temperature. In parallel, single photon avalanche diodes (SPADs) emerged in the area of single photon sensors [11]. The SPAD is a single photon detector operated in Geiger mode. Its optical sensing part is equivalent to a SiPM microcell. The layout of a SPAD differs from the one of a SiPM, as it also includes integrated active quenching electronic components [12]. In other words, the SiPM is equivalent to an array of SPAD-like microcells with passive quenching.

SiPM and SPAD substituted the photomultiplier tubes as low photon flux sensors in a large variety of applications, ranging from scintillator-based high energy physics to nuclear medicine equipment, radiation detectors, lidar systems in the automotive industry, and wearable devices, among others [13].

Recent advances in the conception of SiPM and SPAD are based on the investigation of the possibility of a full implementation of the photo-detector within standard CMOS, which enables the monolithic integration of read-out electronics and photo-detector on the same chip, with a significant reduction of power consumption and simplification of the operational conditions. Moreover, the use of standard CMOS technology facilities reduces the cost of the sensor, allowing an effective and stable mass production for industrial use.

**Figure 1.** Schematics of a modern silicon photomultiplier (SiPM), composed of an array of single photon avalanche diode (SPAD)-like microcells with passive quenching.

The production of modern SiPM sensors within the standard CMOS process has a strong impact on the development of advanced integrated sensors for the detection of low photon flux and ionizing radiation. Further future implications are associated to the CMOS 3D-interconnection [14], which can improve the detection efficiency, as it was shown, by way of example, in the 130 nm Globalfoundries/Tezzaron [15] node. Within this technology, it is possible to develop new digital avalanche pixel structures, which provide a direct access to each pixel. The avalanche pixel image sensors and the avalanche pixel tracking sensors use this technology for low photon flux and ionizing radiation, respectively [16,17]. The application of CMOS SPAD sensor solutions to digital SiPM was demonstrated among others in the 800 nm [10] and 350 nm [18].

The rules imposed by the CMOS technology represent a limitation to the performances of the developed sensors. SiPM and SPAD may suffer localized breakdown conditions on the locally concentrated high electric field at the junction edges. The use of guard ring structures around the sensitive area of each microcell is mandatory in this respect in order to obtain a uniform electric field across the whole sensitive area. The CMOS technology offers few possibilities of implementing such guard rings [19–22]. By way of example, SPAD, SPAD arrays, and SiPM detection structures with several possible layout techniques for the implementation of guard rings were successfully implemented in 800 nm [10,23–30], 700 nm [31], 500 nm [32,33], 350 nm [18,34–46], 180 nm [47–49], 150 nm [50], 130 nm [15,51–55], and 90 nm [56,57] CMOS nodes, and were used to detect single photon signals on the basis of the avalanche breakdown process. Two main limitations of the CMOS technology remain; namely, the higher dark rate and the lower photon detection efficiency with respect to the custom-technology-based conventional SiPMs. As a possible solution, the mask set of CMOS processes is often enlarged with specific implantations, in order to allow the overlap between highly-doped and low-doped regions and to correct the doping profiles of the standard CMOS wells [58].

In this paper, we present a SiPM structure realized in 180 nm CMOS BCDLite technology at Globalfoundries. The CMOS process is used without any customization. We investigate the possibilities and the remaining limitations of this approach, as compared to SiPMs obtained both with custom-technology and in other standard CMOS nodes. This issue is supported by a SILVACO model of the detection structure and by a series of experimental results in dark and light conditions.

#### 2. Materials and Methods

#### 2.1. Simulation of SiPM

SiPM transient simulation is performed using the SILVACO suite [59]. We consider a p<sup>+</sup>/n-well diode structure composed of the typical doping concentrations offered by 180 nm CMOS technology. On a starting n-epitaxial layer with concentration  $10^{15}$  cm<sup>-3</sup>, a gaussian shaped n-well is formed with maximal concentration  $2.9 \times 10^{17}$  cm<sup>-3</sup> at a depth of 436 nm. The p<sup>+</sup> implantation in the n-well has also a gaussian profile with maximal concentration  $3.02 \times 10^{20}$  cm<sup>-3</sup> at a depth of 91 nm. The junction depth between p<sup>+</sup> implantation and n-well is 142 nm.

The simulation includes the main physical processes involved in the SiPM operation. The electric field strength in the detection structure as a function of the total charge density distribution is governed by Poisson's equation. When a microcell is biased in reverse mode, a depletion region is formed between the p- and n-doped regions. The thickness of the depletion region is approximately 1  $\mu$ m. Within the depletion region, an electric field with maximal value of approximately  $10^5$ – $10^6$  V/cm is formed.

The continuity equation for the evaluation of the density of both carrier species includes generation and recombination mechanisms. In radiative recombination processes such as spontaneous or stimulated recombination, an electron is captured back in the valence band, with a consequent emission of respectively one or two photons. In non-radiative recombination processes, described by the Shockley-Read-Hall [60] and three-particle transition Auger models [61], the excess energy of the electrons is released respectively to phonons or to other carriers. In both radiative and non-radiative recombination processes, the excess energy can eventually be transferred to electrons, which are released in the conduction band. This process is naturally included in the recombination rates at equilibrium. The phonon excitation or the photons induced by recombination may in fact provide the necessary energy to an electron in the valence band to be released in the conduction band. Because of the properties of the Fermi distribution function of carriers in silicon, the process of electron-holes generation through recombination is temperature-dependent and is often called thermal generation of electron/hole pairs.

Although in normal conditions these processes would bring the junction back to the equilibrium of the doping concentrations, in the SiPM the produced electron/hole pairs are accelerated in the strong electric field and can trigger an avalanche multiplication chain due to the impact ionization process, which we include following the Selberherr's model [62].

A more precise estimation of the involved processes requires the calculation of the carrier's temperature, which we perform with the energy balance transport model. The thermal diffusivities of electrons and holes derive from the frictional interaction of carriers with lattice and among themselves. Carriers are accelerated by the electric field but lose momentum due to scattering processes, including phonon, carriers, and impurity scattering, surface and material imperfections. This effect is parameterized with a carrier mobility parameter, which is a function of electric field, lattice temperature, and doping concentration, and defines the carrier's thermal diffusivity. In the low electric field regions of the detection structure, the relation between mobility and carrier concentration is included in the model through an experimental look-up table. When the electric field magnitude increases, the mobility depends on the strength of the electric field parallel to the current flow. Such dependence is parameterized using the Caughey and Thomas expression [63]. Relaxation times for energy losses due to the interaction of carriers with the lattice are also included, with characteristic relaxation times on the order of 1 ps. Finally, in heavy-doped regions, effects due to decreased band-gap separation are included according to [64].

The avalanche is self-sustaining, and a quenching mechanism is needed in order to recover to the first stability state of the SiPM. We opt for a passive quenching technique, using an external quenching resistor integrated in each SiPM microcell. The quenching resistor is included in the simulation as an external passive element. The current flow through the resistor causes a voltage drop on the junction, which reduces the actual junction bias to a value lower than the breakdown voltage. From the point of view of carriers kinematics modelling, the avalanche charge crowds within the depletion region and reduces the electric field, thus quenching the avalanche. The function of the large quenching resistor is indeed the limitation of the charge which can flow outside of the device. After the quenching occurs, the SiPM transits back to the initial state within a recovery time determined by the size of the junction capacitance and of the quenching resistor. Parasitic capacitance is not included in the model.

We calculate two variables in the simulation. The first is the current flowing in the circuit composed of the power supply, diode, and quenching resistor. The second is the voltage measured on a 50  $\Omega$  load resistor included in series after the diode and terminated to ground.

The micro-cell size is 50  $\mu$ m × 50  $\mu$ m. The computation is performed using adaptive space and time meshes, with a minimal required mesh size of 0.02  $\mu$ m and time steps of  $10^{-2}$  ps in order to achieve the required precision.

# 2.2. Fabrication of SiPM

The GLOBALFOUNDRIES (GF) 180 nm BCDLite process is an advanced mixed-signal CMOS process providing six metal layers, two polysilicon layers, high-resistivity polysilicon, and two types of transistor gates (3.3 V and 5 V). As with most of the available 180 nm standard CMOS processes at modern foundries, it does not offer an optical coupling (OPTO) module and a passivation layer also covers the sensitive region. This work is thus the basis for a discussion with other silicon facilities, which are always open to giving access to additional non-standard OPTO modules also at smaller scale. From a technological point of view, we also chose this process because it is used for standard electronics components (mainly for the automotive industry), and we aim at demonstrating that a prototype SiPM sensor can be obtained in full compatibility with such electronics. Although the process is also available also through multi-project wafer runs (which offer inexpensive prototyping), we opted for an engineering run, which has the advantage of a better customization.

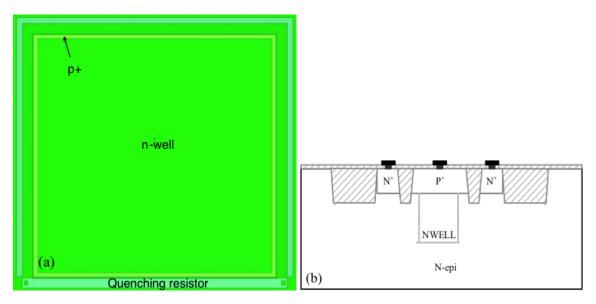

The photodetector structure is based on an n-epitaxial layer, on which the SiPM sensor is formed. Figure 2 shows the layout and the cross-section of one SiPM microcell implemented in the GF 180 nm BCDLite process. We note that in designing such a device, only standard masks provided by the technology are used. The microcell consists of a 50  $\mu$ m  $\times$  50  $\mu$ m n<sup>+</sup>/p-well junction. GF does not share the exact doping of the wells with the customers.

**Figure 2.** (a) Layout of a SiPM microcell in GLOBALFOUNDRIES (GF) 180 nm BCDLite process; and (b) cross-section of the microcell structure.

A virtual guard ring  $p^+/n$ -epi is formed on the periphery of the sensitive avalanche area in order to avoid the spontaneous triggering of breakdown avalanche in the high-gradient electric field on the periphery of the structure. Such a combination violates the inclusion rules of the p-well and  $n^+$  layers. This is the only needed violation of the standard design rules.

The shallow trench isolation (STI) surrounding the sensitive area of the avalanche pixel sensor is provided automatically by the CMOS technology rules. In our case, the STI contributes to the electric isolation of individual avalanche pixel sensor, allowing the necessary electric crosstalk protection of the SiPM microcells. The STI can be used functionally as a guard ring, physically removing the peripheral regions of the  $p^+/n$ -junction [29,46]. Up to now, this option is under investigation, due to the problem of generation of additional leakage current [65].

In order to reduce the thickness of silicon oxide deposited on the active area of the sensor, we use only three metal layers out of the six available in the process.

As shown in the previous section, the avalanche breakdown process in the proposed p/n-junction structures is self-sustaining and requires a special quenching mechanism. In our design, the quenching element is passive. A 250 k $\Omega$  quenching resistor is implemented in the structure outside of the sensitive area on the basis of the high resistive polysilicon process. The resistor width is 0.8  $\mu$ m, and its length approximately 50  $\mu$ m.

On the wafer we produce single microcells test structures as well as SiPM sensor prototypes, consisting of an array of  $20 \times 20$  microcells, connected in parallel, with common output. The SiPM prototype is designed in planar structure. The common cathode and anode are placed at the corners of the microcells array, as opening pads within the SiPM area.

## 3. Characterization Results

Two series of measurements have been carried out for the SiPM sensor prototype: a static and a dynamic characterization, including noise and light response studies. The benchmarking of the experimental results needs to follow a twofold approach. On the one side it is needed to benchmark against the mature available SiPMs, which are not always developed in standard CMOS technology but in dedicated lines with additional optimized masks. This first comparison allows us to understand how far the standard CMOS process is used in this work from the behaviour of specifically optimized processes for good-performing SiPM. On the other side it is needed to benchmark against other experimental attempts of using standard CMOS processes for the production of SiPM. This second comparison allows us to understand how the chosen CMOS technology process performs with respect to other available ones. A selection of representative examples is reported in Table 1.

| Techn.<br>Node<br>(nm) | Pixel<br>Size<br>(µm <sup>2</sup> ) | Typical<br>Operation<br>(V) | Gain                      | Dark Count<br>@typ. bias<br>(KHz/mm <sup>2</sup> ) | Cross-talk<br>(%) | PDE<br>@410 nm<br>(%) |

|------------------------|-------------------------------------|-----------------------------|---------------------------|----------------------------------------------------|-------------------|-----------------------|

| (11111)                | (μ)                                 | (v)                         |                           | (KHZ/IIIII )                                       | (/0)              | ( /0)                 |

| 800 [10]               | 2500                                | BV + 1.5                    |                           | $100 	imes 10^5$                                   |                   | 15 (estimated)        |

| 800 [30]               | 2500                                | $(19.5)_{BV} + 3$           |                           | $3	imes 10^6$                                      |                   | 20                    |

| 800 [30]               | 2500                                | $(17.5)_{BV} + 3$           |                           | $4	imes 10^5$                                      |                   | 25                    |

| 800 [30]               | 2500                                | $(19.5)_{BV} + 2$           |                           | $3 	imes 10^3$                                     |                   | 25                    |

| 500 [32]               | 484                                 | $(16.7)_{BV} + 1.5$         |                           | <120                                               |                   | 15 (estimated)        |

| 350 [41]               | 2000                                | $(18.9)_{BV} + 1$           |                           | $2	imes 10^4$                                      | 2.6               | 1.5                   |

| 350 [44]               | 2500                                | $(25)_{BV} + 6$             | $15 	imes 10^6$           | 503                                                | 33.5              | 34                    |

| 350 [43]               | 913                                 | $(26)_{BV} + 3$             |                           | $1.19 	imes 10^3$                                  | 2                 |                       |

| 350 [18]               | 3185.47                             | $(27.5)_{BV} + 3$           |                           | 75-100                                             |                   |                       |

| 180                    | 2500                                | $(12)_{BV} + 2$             | $1.4 	imes \mathbf{10^6}$ | $20	imes 10^3$                                     | 40                | 1.3                   |

| 180 [49]               | 1024                                | $(10.3)_{BV} + 0.95$        |                           | $27 	imes \mathbf{10^3}$                           |                   | 4                     |

| 130 [15]               | 324,900                             |                             |                           |                                                    |                   |                       |

| SensL [67]             | 100-2500                            | $(24.4)_{BV} + 2.5$         | $4.3	imes10^4$            | 30-100                                             | <2                | 40                    |

| Hamamatsu [9]          | 625–10,000                          | $(65)_{BV} + 2.6$           | $1.26 	imes 10^6$         | 500                                                |                   | 40                    |

**Table 1.** Comparison of the results obtained in this paper, using a 180 nm GF BCDLite CMOS process (in bold), with a selection of SiPMs obtained with standard CMOS technologies (upper part) and with custom-technology (lower part). The breakdown voltage (BV), gain, dark count rate and photon detection efficiency (PDE) at 410 nm are shown when available.

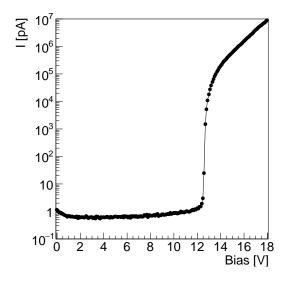

#### 3.1. Static Characterization

We start characterizing the single microcell by evaluating the static current–voltage characteristic in reverse bias mode of operation. The experiment is performed on the single microcell test structure at wafer level. A Keithley 2636 A source meter, connected to a computer, obtains measurements of current in reverse mode. This experiment is achieved by generating a sweep voltage between 0 V and 18 V, then measuring the current and limiting it to 20  $\mu$ A in order to avoid damaging the device. The current versus voltage characteristics reveals the breakdown voltage and the dark current of the sensor.

Figure 3 shows the measured I-V characteristics of the microcell test structure in reverse mode. The structure exhibits a dark current below a few picoamperes before avalanche breakdown. At breakdown, the current rises abruptly up to a few microamperes. After breakdown, it gets limited by the quenching resistor and rises linearly. The breakdown voltage is approximately 12 V. The I-V curve of the SiPM prototype follows the results of the test microcell, without any deviation or unexpected behaviour. It is necessary to note here that the current measured in a static I-V curve represents the average of the current of a certain number of alternating dark pulses and quiescent state current levels within a 1 s time window.

Figure 3. Current-voltage characterization of the SiPM microcell in dark condition.

The sharp rising edge of the breakdown in the I-V curve is also showing that there is no additional leakage current in the structure, which usually deteriorates the shape of the I-V curve [65]. In comparison with the custom-technology available SiPM, as shown on Table 1, the breakdown voltage obtained with the 180 nm GF BCDLite CMOS process is lower. This is because the technology lines specialized to the SiPM production introduce specific processes and additional masks in order to optimize the concentration of the wells forming the active area of the detector.

As reported in Table 1, the result is consistent with a similar SiPM obtained at the 180 nm CMOS technology node [49]. Breakdown voltages ranging from 10 V to 14 V are usually obtained at a scale lower than 180 nm, as in 90 nm [56,57] and 180 nm [20] CMOS nodes. This value depends on the doping of the standard CMOS wells, which range from  $2 \times 10^{17}$  to  $5 \times 10^{17}$  cm<sup>-3</sup>.

### 3.2. Dynamic Characterization

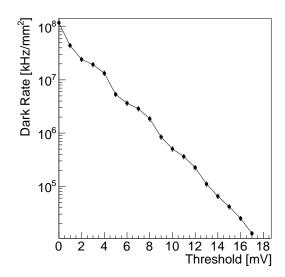

Based on the static characterization results, we performed a dynamic characterization of the SiPM prototype. A first series of measurements addresses the problem of dark rate in SiPM realized in CMOS technology framework. A second series of measurements is performed in light illumination condition.

#### 3.2.1. Noise Study

We measure the dark count rate by counting the number of avalanche signals produced in the SiPM sensor operated at the fixed bias voltage of 14 V, corresponding to 2 V above breakdown. The dark count rate is measured at room temperature and in dark conditions. The voltage amplitude of the signal

of the SiPM is measured on a 50  $\Omega$  load resistor. The output voltage is connected to a fast amplifier, based on a two-stage voltage amplifier obtained with the GALI 5+ wide-band monolithic chip [66]. The total amplification gain is adjusted to 10 with a voltage divider between the two amplification stages. The signal is sent to a threshold discriminator (CAEN N844). The number of pulses above threshold registered within a 1 s observation time window.

The measured dependence of the count rate versus signal amplitude is shown in Figure 4. The error bars represent the standard deviation of the measurement repeated on a set of 20 randomly selected chips produced on the same wafer dice. We observe a series of structures with decreasing amplitude. The first structure corresponds to the level of electronic noise, the second structure corresponds to one dark rate pulse, the *n*-th structure corresponds to n - 1 coincident pulses from independent cells within the observation time window. The probability of measuring a large number of coincident pulses is increased by optical cross-talk, being the electric cross-talk suppressed by the STI. The dark rate at a threshold of 0.5 and 1.5 pulse amplitude is respectively  $20 \times 10^6$  kHz/mm<sup>2</sup> and  $10 \times 10^6$  kHz/mm<sup>2</sup>. The optical cross-talk can be estimated from the ratio of the population of these levels as approximately 50%.

**Figure 4.** Dependence of the dark count rate of the SiPM prototype versus signal threshold at 14 V (2 V overvoltage) at 25°.

In comparison with the custom-technology SiPM benchmarks reported in Table 1, the obtained dark count rate is approximately 100 times larger. Although the operation over-voltage is within the value of the mature SiPM technology, the absolute bias voltage is much lower, as reported in the previous section. At such low breakdown voltage, the tunneling effect plays an important role and significantly deteriorates the dark count rate of the sensor. The degradation of the dark count rate in a standard CMOS process is a well-known problem. With reducing node scale, the wells concentration is increasing, with a consequent decrease of the breakdown voltage of any junction formed in the well. The design of a pn junction for SiPM sensors in modern CMOS technology faces the arising of tunneling effect, which is dominant for silicon at voltages lower than approximately 10 V [57]. This physics mechanism, together with the presence of STI and lower annealing temperature used at smaller scales, increases the amount of free electrons, which reach the conduction band spontaneously, deteriorating the noise performance of the SiPM sensor. The dark rate obtained in this study is compatible with the results at the 180 nm CMOS technology node [49].

Table 1 shows that SiPMs realized in CMOS technology generally exhibit a higher dark rate than SiPMs in custom-technology, due to either STI or higher doping concentration. An increase of the dark count rate was observed, for example, in the study at 350 nm and 90 nm CMOS technology

node [35,57]. This is addressed in [58] as one of the main reasons for the introduction of additional masks in the fabrication of SiPM sensors on the basis of CMOS processes. The cross-talk is higher than in SiPMs with implemented optical trenches [67], suggesting that proper optical trenches need to be implemented for a SiPM with better performance.

### 3.2.2. Light Study

We report here the measurement of packaged samples of the SiPM prototype in response to light. The experimental setup is composed of a fast LED with wavelength 550 nm. The amplitude of the driving pulse of the LED is adjusted with the programmable Keysight 81133A (Keysight, Santa Rosa, CA, USA) pulse pattern generator. A pulse width of 10 ns is chosen, approximately ten times less than the recovery time of the SiPM. The light pulses are delivered to the operation position in the light protected area by an optical fiber. The SiPM and the light source are kept at a relative distance of 1 cm. The optical table components provide an alignment precision of 0.1 mm between SiPM and optical source. The temperature of the experimental setup is controlled and kept constant at 25 °C.

In order to calibrate the optical source, the C-Series SiPM by sensL, with a total area of  $1 \text{ mm} \times 1 \text{ mm}$  is used in the same experimental setup. We detected a total of 80 photons. Considering that the photon detection efficiency of the used SiPM is approximately 25% at 550 nm, we estimate an average number of approximately 320 photons at the surface of the SiPM.

The voltage amplitude of the signal of the SiPM is measured on a 50  $\Omega$  load resistor connected to a fast amplifier, based on a two-stage voltage amplifier obtained with the GALI 5+ wide-band monolithic amplifier [66]. The total amplification gain is adjusted to 15 with a voltage divider between the two amplification stages. The charge of the signal is measured within an integration gate of 100 ns using the CAEN V1180 QDC in the VME Frame and stored in the control computer.

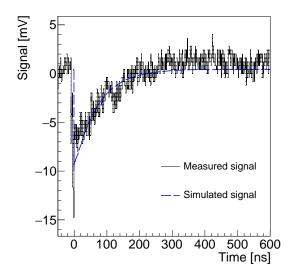

Figure 5 shows the measured signal corresponding to a single photon or to a thermally generated dark pulse. The signal exhibits a rise-time of approximately 120 ps and a characteristic recovery time of 67 ns. These timing properties are consistent with a quenching resistor of 250 k $\Omega$  and a capacitance of approximately 0.3 pF. The corresponding simulated signal—estimated on a 50  $\Omega$  load resistor, included in the simulation, and rescaled with the amplification stage used in the experiment—is shown in Figure 5 as a dotted blue line. The experimental observation is in agreement with the theoretical expectation. The impedance mismatch between diode, quenching resistor, and load resistor is responsible for the fast spike at the signal front in response to the fast quenching time. It is more pronounced in the data than in the simulation, because the parasitic capacitance is not included in the model.

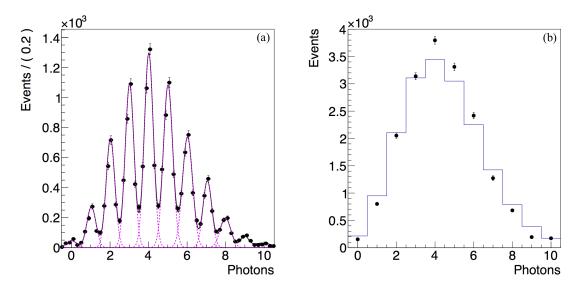

Figure 6a shows the detected photon flux spectrum. On the *x* axis the measured charge is divided by the electron charge and the gain in order to represent the number of detected photons. The histogram consists of colorredhighly resolved peaks correspondeing to the number of detected photons. Each avalanche pixel detects one photon and provides as output the standard signal corresponding to a single photon. The common output of the SiPM is the analog sum of the signals from each avalanche pixel. In this condition, the first peak corresponds to 0 detected photons (electronic noise pedestal), the second one corresponds to 1 detected photon, the (n + 1)th one to *n* detected photons.

The number of peaks contains the information about the number of detected photons. The separation between two successive peaks has a constant magnitude and corresponds to the total number of electrons produced in the avalanches process.

The analysis of the single photon spectrum is performed by fitting the spectrum with a multi-gaussian function composed of equally spaced gaussians. We follow the fitting technique reported in [68]. The fit result is shown in Figure 6a.

As a cross-check, we calculated the charge contained in the signal shown on Figure 5, and we verify that it is consistent with the average charge of the 1-photon peak in the spectrum in Figure 6a, which is measured as the fitted constant distance between the peaks. It corresponds to the internal

amplification gain, and is estimated as  $G = (1.406 \pm 0.003) \times 10^6$ . It is consistent with the expected values obtained in previously designed devices, as reported in Table 1.

**Figure 5.** Simulated (blue dotted line) and measured (dark continuous line) signal of the SiPM prototype in response to a detected optical photon or a thermally generated electron/hole pair.

**Figure 6.** (a) Spectrum of the low photon flux detected by the SiPM prototype. The histogram is fit with a multi-gaussian fit (continuous line) with separately fitted areas (dotted line); (b) Statistical distributions of the number of events (area) of each peak in the spectrum and theoretical Poisson distribution.

The resolution of the photon peaks is quantified using the fitted width  $\sigma_1$  of the 1-photon-peak and its distance from the pedestal  $\mu_1 - \mu_0$ :

$$R = \frac{\sigma_1}{\mu_1 - \mu_0} \tag{1}$$

In the proposed SiPM we obtain  $R = (23.4 \pm 0.1)\%$ . The photon peak resolution is determined by the electronic noise of the experimental setup and by the uniformity of the microcells. While the former aspect can be improved with dedicated low-noise readout electronics, the latter aspect is affected by

two main intrinsic parameters of the CMOS technology process, namely the precision of the quenching resistor and the precision of the doping profiles in overlapping structures. It is useful to analyze here the contribution of these two features of the CMOS process.

The quenching resistor is obtained in the CMOS technology with a high resistance polysilicon (HRP). The doping stability of the HRP for different shapes and widths of the resistor is a common problem in CMOS silicon foundries. In 180 nm nodes and below, the precision of the resistor degrades with smaller length and width. The problem here is that the HRP is used in CMOS fabs mainly for digital electronic components, which do not need a high accuracy. The uniformity of the value of the resistor can have a spread of up to 10% in CMOS silicon foundries dedicated to digital electronics components. Analog applications as passive quenching in SiPM sensors require a high-quality HRP process, which is not always available at standard CMOS foundries.

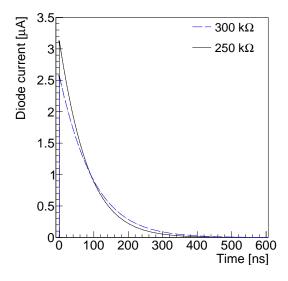

In order to study the effect of a change of the quenching resistor, we perform a transient simulation of the proposed structure using two sets of resistors, 250 k $\Omega$  and 300 k $\Omega$ . We report in Figure 7 the diode current corresponding to a single photon or to a thermally generated dark pulse. The current is flowing in the circuit composed of the diode, the bias source, and the quenching resistor. In both cases, the total charge contained in the signal is approximately  $1.4 \times 10^6$  electrons. The two signals have different peak amplitude, respectively 3  $\mu$ A and 2.5  $\mu$ A and decay time 78 ns and 93 ns. We conclude that a pixel-by-pixel non-uniformity of the quenching resistor does not affect the gain spread and the photon peak resolution, but has a negative impact on the overall time resolution of the detector.

**Figure 7.** Simulated current of a SiPM sensor in response to a single photon or a thermally produced electron/hole pair for 250 k $\Omega$  (black continuous line) and 300 k $\Omega$  (blue dotted line) quenching resistor.

Another significant technological issue when using the CMOS technology processes is the uniformity of the doping. In fact, the doping concentration of the wells affects the breakdown voltage. Power devices, logic, and analog electronic circuits do not require a precise breakdown voltage, as they operate at much lower biases. In these applications, the main optimization parameters to be considered are leakage current and electrical isolation, which should be under a specified tolerance threshold. The application of the standard CMOS processes to the fabrication of the SiPM sensor requires a much stronger constraint in terms of the needed tolerance of the doping profile.

Current implantation and annealing techniques guarantee a good uniformity of the well within the sensor. However, the problem here is at the edges of the junction, as the photodiode should be surrounded by a suitable guard ring (GR) to smooth the charge concentration and avoid the occurrence of local breakdown. Such guard rings are often implemented as regions with smaller doping levels (n-well structures or p-well implants) surrounding the active part of the sensor and lowering the electric field at the borders of the diode [29,46]. Implementing such GR structures at CMOS nodes smaller than 250 nm requires the violation of standard rules and may create non-uniformities in the obtained wells—in particular at the annealing stage—if the CMOS fabrication processes are used without any special consideration of this modified requirement.

We performed a transient simulation of a SiPM structure, modifying the doping concentration of the n-well. We observed that a change of 0.5% in the doping concentration contributes to a change of approximately 1% in the micro-cell gain. We conclude that a pixel-by-pixel non-uniformity of the doping concentration affects the gain spread and hence deteriorates the photon peak resolution.

As the photon peaks are well-visible and detected with a resolution of  $(23.4 \pm 0.1)$ %, it is possible to conclude that although some standard rules are violated, the pixel-by-pixel non-uniformity is not dramatically affecting the gain spread in the design of the 50 µm side pixels at the Globalfoundries 180 nm CMOS node under investigation in this paper. This observation agrees with the results obtained, among others, at the Globalfoundries 130 nm CMOS node [15]. However, dedicated tests will be needed to experimentally verify the pixel-by-pixel non-uniformity in SiPMs with smaller or larger microcell size obtained at the same 180 nm technology node.

A second aspect of the spectrum in Figure 6a is that the area under each peak reflects the Poisson statistics of the photon detection in the SiPM structure and the contribution of the electronic noise. The average number of detected photons  $\mu$  described by the Poisson distribution is calculated from the number of events of the pedestal peak  $N_0$  and the total number of events N, applying the reconstruction formula under the hypothesis of a Poisson-distributed detected light:

$$\mu = \log \frac{N}{N_0} \tag{2}$$

The average number of detected photons within the 100 ns time window is  $\mu = 4.34 \pm 0.01$ . Considering that, as stated above, the expected number of photons at the SiPM surface is approximately 320, we estimate a photon detection efficiency of approximately 1.3%. This result is below the expectation and is consistent with similar studies in standard CMOS technology processes. We observe in Table 1 that a photon detection efficiency lower than 4% at 420 nm due to the absence of an optical window and to the presence of a passivation layer are reported in the development of CMOS SiPM at the 350 nm HV AMS [41] and 180 nm [49] nodes.

Finally, it is necessary to state here that the result obtained using Formula (2) is only an approximation. In fact, as reported in the previous section, the sensor considered here exhibits a sizeable dark rate. It is hence expected that the response to the light source is affected by it. A statistical analysis of the single photon spectrum allows a better understanding of this phenomena. In Figure 6b we compare the theoretical expected Poisson distribution with the number of events (the area) of each peak in the experimental data obtained in the fit on Figure 6a. We observe a deviation between theory and experimental data, consisting approximately of a 15% excess of events at values higher than three photons. This shift in the observed distribution is due to dark rate and cross-talk, which cannot be neglected in this device. Correction schemes to this common problem in the SiPM application are reported in the literature [69,70].

# 4. Conclusions

We have presented an investigation concerning a silicon photomultiplier designed with the GF 180 nm BCDLite process. We found that with a minimal violation of the design rules (but still using only the standard production masks), it is possible to obtain a structure with a good photon signal resolution following the expectation of mature SiPM technology. However, the SiPM exhibits reduced photon detection efficiency due to the absence of an optical window in the GF 180 nm BCDLite process, high dark rate due to the tunneling effect at low breakdown voltage, and a relatively high cross-talk. We conclude that the addition of a dedicated OPTO process, of a mask for the tuning of the well doping in the sensor area and of optical isolation trenches is still needed in order to make a SiPM on one

hand competitive with the mature SiPM technology and on the other hand fully compatible with the standard electronics developed in CMOS technology.

**Acknowledgments:** The authors acknowledge the support of the project 61604059 by the Natural Science Foundation of China.

**Author Contributions:** N.D. and Q.X. conceived and designed the experiments and made the sensor layout; X.Z. analysed the data and performed the simulation.

**Conflicts of Interest:** The authors declare no conflict of interest. The funding sponsors had no role in the design of the study; in the collection, analyses, or interpretation of data; in the writing of the manuscript, and in the decision to publish the results.

# Abbreviations

The following abbreviations are used in this manuscript:

- BV Breakdown Voltage

- GF GLOBALFOUNDRIES

- GR Guard Ring

- HRP High Resistance Polysilicon

- MRS Metal Resistor Semiconductor

- OPTO Optical coupling module

- PDE Photon Detection Efficiency

- QDC Charge Digital Converter

- SiPM Silicon Photomultiplier

- SPAD Single Photon Avalanche Diode

- STI Shallow Trench Isolation

# References

- 1. Gasanov, A.; Golovin, V.; Sadygov, Z.Y.; Yusipov, N.Y. Avalanche photodetector based on metal-resistive-layer semiconductor structures. *Pisma V Zhurnal Tekh. Fiz.* **1988**, *14*, 706–709.

- 2. Shushakov, D.A.; Shubin, V.E. New Solid State Photomultiplier. In Proceedings of the Optoelectronic Integrated Circuit Materials, Physics, and Devices, Bellingham, WA, USA, 24 April 1995; pp. 544–554.

- 3. Sadygov, Z. Avalanche Detector. Russian Patent RU 2102820, 10 October 1996.

- 4. Golovin, M.; Akindinov, A.; Grigorev, E.; Martemyanov, A.; Polozov, P. New results on mrs apds. *Nucl. Instrum. Methods A* **1997**, *387*, 231–234.

- 5. Saveliev, V.; Golovin, V. Silicon avalanche photodiodes on the base of metal-resistor-semiconductor (mrs) structures. *Nucl. Instrum. Methods A* **2000**, *442*, 223–229.

- 6. Buzhan, P.; Dolgoshein, B.; Ilyin, A.; Kantserov, V.; Kaplin, V.; Karakash, A.; Pleshko, A.; Popova, E.; Smirnov, S.; Volkov, Y. An advanced study of silicon photomultiplier. *ICFA Instrum. Bull.* **2001**, *21*, 28–41.

- Piemonte, C.; Battiston, R.; Boscardin, M.; Dalla Betta, G.-F.; Del Guerra, A.; Dinu, N.; Pozza, A.; Zorzi, N. Characterization of the first prototypes of silicon photomultiplier fabricated at itc-irst. *IEEE Trans. Nucl. Sci.* 2007, 54, 236–244.

- 8. Stewart, A.; Saveliev, V.; Bellis, S.; Herbert, D.; Hughes, P.; Jackson, J. Performance of 1 mm<sup>2</sup> silicon photomultiplier. *IEEE J. Quant. Electron.* **2008**, *44*, 157–164.

- 9. Ghassemi, A.; Sato, K.; Kobayashi, K. *MPPC*; Hamamatsu Technical Note. KAPD9005E01; Hamamatsu Photonics: Hamamatsu, Japan, 2017.

- 10. Nolet, F.; Rhéaume, V.-P.; Parent, S.; Charlebois, S.A.; Fontaine, R.; Pratte, J.-F. A 2d proof of principle towards a 3D digital SiPM in HV CMOS with low output capacitance. *IEEE Trans. Nucl. Sci.* 2016, *63*, 2293–2299.

- 11. Cova, S.; Lacaita, A.; Ghioni, M.; Ripamonti, G.; Louis, T. 20 ps timing resolution with single-photon avalanche diodes. *Rev. Sci. Instrum.* **1989**, *60*, 1104–1110.

- Villa, F.; Bronzi, D.; Zou, Y.; Scarcella, C.; Boso, G.; Tisa, S.; Tosi, A.; Zappa, F.; Durini, D.; Weyers, S. CMOS SPADs with up to 500 μm diameter and 55% detection efficiency at 420 nm. *J. Mod. Opt.* 2014, 61, 102–115.

- 13. D'Ascenzo, N.; Saveliev, V. The new photo-detectors for high energy physics and nuclear medicine. In *Photodiodes-Communications, Bio-Sensings, Measurements and High-Energy Physics;* InTech: Rijeka, Croatia, 2011.

- 14. Patti, R.S. Three-dimensional integrated circuits and the future of system-on-chip designs. *Proc. IEEE* 2006, 94, 1214–1224.

- Vilella, E.; Alonso, O.; Dieguez, A. 3D integration of geiger-mode avalanche photodiodes aimed to very high fill-factor pixels for future linear colliders. *Nucl. Instrum. Methods Phys. Res. Sect. A Accel. Spectrometers Detect. Assoc. Equip.* 2013, 731, 103–108.

- D'Ascenzo, N.; Marrocchesi, P.; Moon, C.; Morsani, F.; Ratti, L.; Saveliev, V.; Navarro, A.S.; Xie, Q. Silicon avalanche pixel sensor for high precision tracking. J. Instrum. 2014, 9, C03027, doi:10.1088/1748-0221/9/03/C03027.

- 17. Pancheri, L.; Ficorella, A.; Brogi, P.; Collazuol, G.; Dalla Betta, G.-F.; Marrocchesi, P.; Morsani, F.; Ratti, L.; Savoy-Navarro, A.; Sulaj, A. First demonstration of a two-tier pixelated avalanche sensor for charged particle detection. *IEEE J. Electron Devices Soc.* **2017**, *5*, 404–410.

- Fischer, P.; Armbruster, T.; Blanco, R.; Ritzert, M.; Sacco, I.; Weyers, S. A dense spad array with full frame readout and fast cluster position reconstruction. In Proceedings of the IEEE Nuclear Science Symposium and Medical Imaging Conference (NSS/MIC), Seattle, WA, USA, 8–15 November 2014.

- Izhaky, N.; Morse, M.T.; Koehl, S.; Cohen, O.; Rubin, D.; Barkai, A.; Sarid, G.; Cohen, R.; Paniccia, M.J. Development of CMOS-compatible integrated silicon photonics devices. *IEEE J. Sel. Top. Quant. Electron.* 2006, 12, 1688–1698.

- 20. Lee, M.-J.; Rucker, H.; Choi, W.-Y. Effects of guard-ring structures on the performance of silicon avalanche photodetectors fabricated with standard CMOS technology. *IEEE Electron Device Lett.* **2012**, *33*, 80–82.

- 21. Lee, M.-J.; Choi, W.-Y. Effects of parasitic resistance on the performance of silicon avalanche photodetectors in standard CMOS technology. *IEEE Electron Device Lett.* **2016**, *37*, 60–63.

- 22. Sul, W.-S.; Oh, J.-H.; Lee, C.-H.; Cho, G.-S.; Lee, W.-G.; Kim, S.-D.; Rhee, J.-K. Guard-ring structures for silicon photomultipliers. *IEEE Electron Device Lett.* **2010**, *31*, 41–43.

- 23. Niclass, C.; Rochas, A.; Besse, P.-A.; Charbon, E. Toward a 3-D camera based on single photon avalanche diodes. *IEEE J. Sel. Top. Quant. Electron.* **2004**, *10*, 796–802.

- 24. Rochas, A.; Gosch, M.; Serov, A.; Besse, P.; Popovic, R.; Lasser, T.; Rigler, R. First fully integrated 2-D array of single-photon detectors in standard CMPS technology. *IEEE Photonics Technol. Lett.* **2003**, *15*, 963–965.

- Tisa, S.; Zappa, F.; Labanca, I. On-chip detection and counting of single-photons. In Proceedings of the IEEE International Electron Devices Meeting on IEDM Technical Digest, Washington, DC, USA, 5–7 December 2005; pp. 815–818.

- 26. Stoppa, D.; Pancheri, L.; Scandiuzzo, M.; Gonzo, L.; Dalla Betta, G.-F.; Simoni, A. A cmos 3-d imager based on single photon avalanche diode. *IEEE Trans. Circuits Syst.* **2007**, *54*, 4–12.

- 27. Niclass, C.; Rochas, A.; Besse, P.-A.; Charbon, E. Design and characterization of a CMOS 3-D image sensor based on single photon avalanche diodes. *IEEE J. Solid-State Circuits* **2005**, *40*, 1847–1854.

- Stoppa, D.; Pancheri, L.; Scandiuzzo, M.; Malfatti, M.; Pedretti, G.; Gonzo, L. A single-photon-avalanche-diode 3D imager. In Proceedings of the 31st European Solid-State Circuits Conference, Grenoble, France, 12–16 September 2005; pp. 487–490.

- Rochas, A.; Gani, M.; Furrer, B.; Besse, P.; Popovic, R.; Ribordy, G.; Gisin, N. Single photon detector fabricated in a complementary metal-oxide-semiconductor high-voltage technology. *Rev. Sci. Instrum.* 2003, 74, 3263–3270.

- Bérubé, B.-L.; Rhéaume, V.-P.; Parent, S.; Maurais, L.; Therrien, A.C.; Charette, P.G.; Charlebois, S.A.; Fontaine, R.; Pratte, J.-F. Implementation study of single photon avalanche diodes (spad) in 0.8 μm HV CMOS technology. *IEEE Trans. Nucl. Sci.* 2015, *62*, 710–718.

- Pancheri, L.; Stoppa, D. Low-noise CMOS single-photon avalanche diodes with 32 ns dead time. In Proceedings of the 37th European Solid State Device Research Conference, Munich, Germany, 11–13 September 2007; pp. 362–365.

- Habib, M.H.U.; McFarlane, N. A perimeter gated single photon avalanche diode based silicon photomultiplier as optical detector. In Proceedings of the 2015 IEEE 58th International Midwest Symposium on Circuits and Systems (MWSCAS), Fort Collins, CO, USA, 2–5 August 2015; pp. 1–4.

- 33. Gu, J.; Habib, M.H.U.; McFarlane, N. Perimeter gated single photon avalanche diodes: An information theoretic assessment. *IEEE Photon. Technol. Lett.* **2016**, *28*, 701–704.

- 34. Niclass, C.; Sergio, M.; Charbon, E. A Single Photon Avalanche Diode Array Fabricated in 0.35 μM CMOS and Based on an Event-Driven Readout for TCSPC Experiments; SPIE Optics East: Boston, MA, USA, 2006.

- 35. Niclass, C.; Favi, C.; Kluter, T.; Monnier, F.; Charbon, E. Single-photon synchronous detection. *IEEE J. Solid-State Circuits* **2009**, *44*, 1977–1989.

- Tisa, S.; Guerrieri, F.; Tosi, A.; Zappa, F. 100 kframe/s 8 bit monolithic single-photon imagers. In Proceedings of the 2008 38th European Solid-State Device Research Conference, Edinburgh, UK, 15–19 September 2008; pp. 274–277.

- 37. Tisa, S.; Guerrieri, F.; Zappa, F. Variable-load quenching circuit for single-photon avalanche diodes. *Opt. Express* **2008**, *16*, 2232–2244.

- 38. Stoppa, D.; Mosconi, D.; Pancheri, L.; Gonzo, L. Single-photon avalanche diode cmos sensor for time-resolved fluorescence measurements. *IEEE Sens. J.* **2009**, *9*, 1084–1090.

- Arbat, A.; Trenado, J.; Gascon, D.; Vilá, A.; Comerma, A.; Garrido, L.; Diéguez, A. High voltage vs. High integration: A comparison between CMOS technologies for SPAD cameras. In Proceedings of the SPIE Optics and Photonics, San Diego, CA, USA, 19–23 August 2010; Volume 7780.

- 40. Niclass, C.; Favi, C.; Kluter, T.; Gersbach, M.; Charbon, E. A 128×128 single-photon image sensor with column-level 10-bit time-to-digital converter array. *IEEE J. Solid-State Circuits* **2008**, *43*, 2977–2989.

- 41. Vilella, E.; Alonso, O.; Montiel, A.; Vilá, A.; Diéguez, A. A low-noise time-gated single-photon detector in a HV-CMOS technology for triggered imaging. *Sens. Actuators A Phys.* **2013**, *201*, 342–351.

- 42. Nissinen, I.; Nissinen, J.; Lansman, A.; Hallman, L.; Kilpela, A.; Kostamovaara, J.; Kogler, M.; Aikio, M.; Tenhunen, J. A sub-ns time-gated CMOS single photon avalanche diode detector for raman spectroscopy. In Proceedings of the 2011 European Solid-State Device Research Conference, Helsinki, Finland, 12–16 September 2011; pp. 375–378.

- 43. Schwinger, A.; Brockherdea, W.; Hostickaa, B.J.; Vogta, H. CMOS SiPM with integrated amplifier. In Proceedings of the SPIE OPTO, San Francisco, CA, USA, 16 February 2017; p. 101001A.

- 44. Zou, Y.; Villa, F.; Bronzi, D.; Tisa, S.; Tosi, A.; Zappa, F. Planar CMOS analog SiPMs: Design, modeling, and characterization. *J. Mod. Opt.* **2015**, *62*, 1693–1702.

- 45. Vilella, E.; Diéguez, A. A gated single-photon avalanche diode array fabricated in a conventional CMOS process for triggered systems. *Sens. Actuators A Phys.* **2012**, *186*, 163–168.

- Jradi, K.; Pellion, D.; Ginhac, D. Design, characterization and analysis of a 0.35 μm CMOS SPAD. Sensors 2014, 14, 22773–22784.

- 47. Finkelstein, H.; Hsu, M.J.; Esener, S.C. Sti-bounded single-photon avalanche diode in a deep-submicrometer cmos technology. *IEEE Electron Device Lett.* **2006**, *27*, 887–889.

- 48. Faramarzpour, N.; Deen, M.J.; Shirani, S.; Fang, Q. Fully integrated single photon avalanche diode detector in standard cmos 0.18-μm technology. *IEEE Trans. Electron Devices* **2008**, *55*, 760–767.

- 49. Vornicu, I.; Bandi, F.N.; Carmona-Galán, R.; Rodríguez-Vázquez, Á. A CMOS digital SiPM with focal-plane light-spot statistics for DOI computation. *IEEE Sens. J.* **2017**, *17*, 632–643.

- Pancheri, L.; Stoppa, D. Low-noise single photon avalanche diodes in 0.15 μm CMOS technology. In 2011 Proceedings of the European Solid-State Device Research Conference, Helsinki, Finland, 12–16 September 2011; pp. 179–182.

- 51. Richardson, J.A.; Grant, L.A.; Henderson, R.K. Low dark count single-photon avalanche diode structure compatible with standard nanometer scale cmos technology. *IEEE Photonics Technol. Lett.* **2009**, *21*, 1020–1022.

- 52. Gersbach, M.; Maruyama, Y.; Trimananda, R.; Fishburn, M.W.; Stoppa, D.; Richardson, J.A.; Walker, R.; Henderson, R.; Charbon, E. A time-resolved, low-noise single-photon image sensor fabricated in deep-submicron CMOS technology. *IEEE J. Solid-State Circuits* **2012**, *47*, 1394–1407.

- Henderson, R.K.; Richardson, J.; Grant, L. Reduction of band-to-band tunneling in deep-submicron cmos single photon avalanche photodiodes. In Proceedings of the International Image Sensor Workshop (IISW 2009), Bergen, Norway, 22–28 June 2009; pp. 26–28.

- 54. Niclass, C.; Gersbach, M.; Henderson, R.; Grant, L.; Charbon, E. A single photon avalanche diode implemented in 130-nm CMOS technology. *IEEE J. Sel. Top. Quant. Electron.* **2007**, *13*, 863–869.

- 55. Arbat, A. Towards A Froward Tracker Detector Based on Geiger Mode Avalanche Photodiodes for Future Linear Colliders. Ph.D. Thesis, Department Electronics, University Barcelona, Barcelona, Spain, 2010.

- 56. Karami, M.A.; Gersbach, M.; Yoon, H.-J.; Charbon, E. A new single-photon avalanche diode in 90 nm standard CMOS technology. *Opt. Express* **2010**, *18*, 22158–22166.

- 57. Webster, E.A.; Richardson, J.A.; Grant, L.A.; Renshaw, D.; Henderson, R.K. A single-photon avalanche diode in 90-nm CMOS imaging technology with 44% photon detection efficiency at 690 nm. *IEEE Electron Device Lett.* **2012**, *33*, 694–696.

- Durini, D.; Paschen, U.; Schwinger, A.; Spickermenn, A. Silicon based single-photon avalanche diode (SPAD) technology for low-light and high speed applications. In *Photodetectors*; Nabet, B., Ed.; Elsevier: Tokyo, Japan, 2016; pp. 345–371.

- 59. SILVACO. Available online: www.silvaco.com (accessed on 22 September 2017).

- 60. Shockley, W.; Read, W., Jr. Statistics of the recombinations of holes and electrons. Phys. Rev. 1952, 87, 835–842.

- 61. Fossum, J.; Lee, D. A physical model for the dependence of carrier lifetime on doping density in nondegenerate silicon. *Solid-State Electron.* **1982**, *25*, 741–747.

- 62. Selberherr, S. *Analysis and Simulation of Semiconductor Devices*; Springer Science & Business Media: Berlin, Germany, 2012.

- 63. Caughey, D.; Thomas, R. Carrier mobilities in silicon empirically related to doping and field. *Proc. IEEE* **1967**, *55*, 2192–2193.

- 64. Slotboom, J.; De Graaff, H. Measurements of bandgap narrowing in si bipolar transistors. *Solid-State Electron*. **1976**, *19*, 857–862.

- D'Ascenzo, N.; Saveliev, V.; Xie, Q. Design and test of SiPM structures in CMOS technology. In Proceedings of the 2016 4th International Conference on Photonics, Optics and Laser Technology (PHOTOPTICS), Rome, Italy, 27–29 Feberuary 2016; pp. 1–8.

- 66. MiniCircuits. Available online: www.minicircuits.com (accessed on 22 September 2017).

- 67. Datasheet of the SensL MicroC Series. 2015. Available online: http://sensl.com/downloads/ds/DS-MicroCseries.pdf (accessed on 22 September 2017).

- 68. D'Ascenzo, N.; Saveliev, V.; Wang, L.; Xie, Q. Analysis of photon statistics with silicon photomultiplier. *J. Instrum.* **2015**, *10*, C08017, doi:10.1088/1748-0221/10/08/C08017.

- 69. Finocchiaro, P.; Pappalardo, A.; Cosentino, L.; Belluso, M.; Billotta, S.; Bonanno, G.; Di Mauro, S. Features of silicon photo multipliers: Precision measurements of noise, cross-talk, afterpulsing, detection efficiency. *IEEE Trans. Nucl. Sci.* **2009**, *56*, 1033–1041.

- Chmill, V.; Garutti, E.; Klanner, R.; Nitschke, M.; Schwandt, J. On the characterisation of SiPMs from pulse-height spectra. *Nucl. Instrum. Methods Phys. Res. Sect. A Accel. Spectrometers Detect. Assoc. Equip.* 2017, 854, 70–81.

**Sample Availability:** Samples of the SiPM sensor prototypes manufactured and tested as well as the simulation code are available from the authors.

© 2017 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).